先进封装技术详解:Chiplet、CoWoS与HBM背后的设备挑战

核心结论

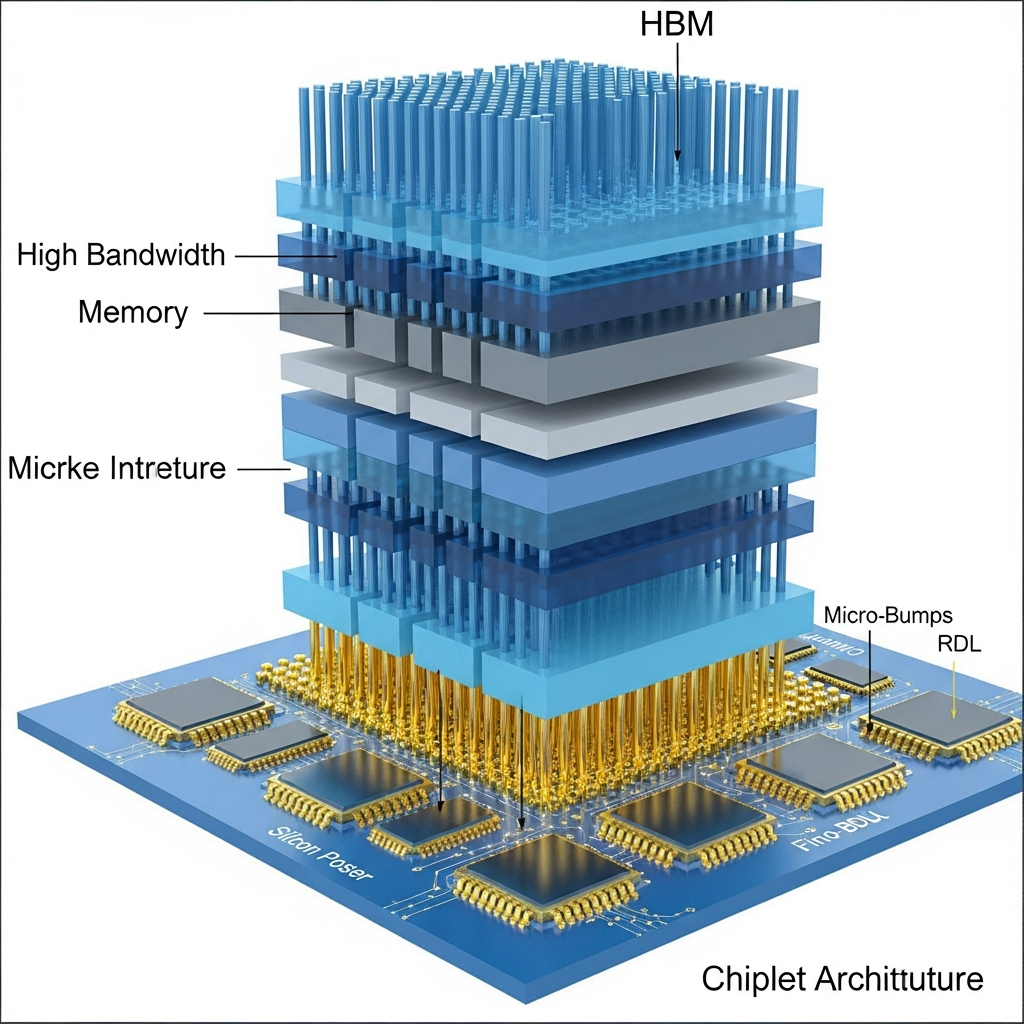

先进封装技术(Chiplet、CoWoS、HBM)正在重塑半导体设备需求。CoWoS产能占台积电先进封装超过20%,HBM堆叠从8层向‖12层演进,设备精度要求提升至亚微米级,AI在工艺控制中的价值显著提升。

2025年以来,”先进封装”成为半导体行业最炙手可热的关键词。NVIDIA、AMD、苹果等芯片巨头纷纷将先进封装视为突破算力瓶颈的核心路径;台积电的CoWoS产能被疯抢,交期一度拉长至超过50周;SK海力士的HBM产线满负荷运转,订单排到了2026年。这一切的背后,是三股力量的交汇:AI大模型对算力和带宽的指数级需求、摩尔定律在先进制程上的经济性放缓,以及Chiplet(小芯片)作为”后摩尔时代”主流技术路线的全面确立。

然而,当行业的聚光灯照向封装架构创新时,一个更深层的问题正在浮出水面——封装设备准备好了吗?从键合精度到翘曲控制,从良率管理到工艺调机,先进封装对设备能力提出了前所未有的极端挑战。本文将系统梳理三大先进封装核心技术,深入分析其对设备端的影响,并探讨AI技术如何帮助封装设备制造商和使用者应对这些挑战。

一、三大先进封装核心技术

1.1 Chiplet:为什么”拆”比”不拆”好

传统芯片设计追求单片集成(Monolithic),将尽可能多的功能集成在一块芯片上。但随着先进制程的成本飙升——台积电3nm的流片费用已超过5亿美元——这条路越来越难走。Chiplet架构的核心理念是“异构拆分”:将一颗大芯片拆分为多个功能模块(小芯片),每个模块可以独立选择最适合的制程节点,最后通过先进封装技术互联组装。

这样做的好处是显著的:

- 成本优化:计算核心用3nm/2nm先进制程,I/O芯片用成熟的12nm/7nm,整体成本可降低30%-50%;

- 良率提升:小芯片的面积远小于单片大芯片,晶圆良率呈指数级提升;

- 灵活组合:同一系列产品可通过不同的Chiplet组合实现差异化,大幅缩短开发周期。

AMD的EPYC系列处理器是Chiplet架构的标杆:第四代EPYC(Genoa)采用多达12颗5nm CCD + 1颗6nm IOD的组合,在服务器市场持续蚕食Intel份额。Intel的Ponte Vecchio GPU则将超过40颗不同工艺节点的Chiplet集成在一个封装中。2023年正式发布的UCIe(Universal Chiplet Interconnect Express)标准,由Intel、AMD、台积电、三星等巨头联合推动,旨在建立Chiplet间互联的开放生态,其1.1版本已支持每毫米带宽密度超过1300 Gbps的die-to-die互联。

1.2 CoWoS:AI芯片的”封装基座”

如果说Chiplet解决了”拆”的问题,那么CoWoS(Chip on Wafer on Substrate)就是解决”装”的问题。这是台积电开发的2.5D封装技术平台,其核心是在芯片和有机基板之间引入一层硅中介层(Silicon Interposer),利用硅的超高布线密度实现多颗芯片之间的高速互联。

CoWoS的技术优势在于:

- 超高互联密度:硅中介层上的布线间距可达0.4μm,远优于传统有机基板的10-20μm;

- 超高带宽:芯片间通信带宽可达TB/s级别,满足AI加速器对数据吞吐的极端需求;

- 信号完整性:硅中介层的低介电常数和短互联长度,确保了高频信号的传输质量。

NVIDIA的H100 GPU采用CoWoS-S封装,将GPU die与6颗HBM3堆叠在同一硅中介层上,中介层面积约为2500mm²。而最新的B200则更进一步,采用台积电第五代CoWoS-L技术,中介层面积突破性地达到约5000mm²,是一块完整12英寸晶圆面积的近7%。据Yole Intelligence预测,全球CoWoS产能需求将从2024年的约30万片/月增长到2026年的超过80万片/月,年复合增长率超过60%。

1.3 HBM:用”堆叠”突破带宽墙

HBM(High Bandwidth Memory,高带宽内存)是先进封装技术在存储领域的极致应用。其核心技术是TSV(硅通孔,Through-Silicon Via)——在DRAM晶圆上垂直打通微米级的导电通孔,然后将多层DRAM die像”三明治”一样堆叠起来,底部通过微凸块与逻辑控制die键合。

HBM3规格支持每堆栈12层DRAM die堆叠(12-Hi),单堆栈容量24GB,带宽达819 GB/s。最新的HBM3E将单堆栈带宽进一步推升至1.18 TB/s,成为NVIDIA B200等新一代AI GPU的标配内存。更值得关注的是,SK海力士已在2025年初开始量产HBM4样品,采用16层堆叠和全新的1024-bit接口,单堆栈带宽有望突破1.6 TB/s。

HBM市场的竞争格局高度集中:SK海力士以约50%的市场份额领跑,三星和美光分别占据约30%和20%。三家厂商都在疯狂扩产——SK海力士2025年的HBM产能预计同比增长超过150%,但仍无法完全满足下游需求。这场”封装军备竞赛”的背后,是对封装设备能力的极限考验。

二、先进封装对设备的极端挑战

2.1 精度要求的量级跃升

传统封装的引线键合(Wire Bonding)和倒装芯片(Flip Chip)技术,键合精度要求通常在±10μm到±25μm范围内。而先进封装彻底改变了这个数量级:

- 混合键合(Hybrid Bonding):铜-铜直接键合的对准精度要求已进入±0.5μm甚至±0.2μm的区间;

- 微凸块(Micro Bump):HBM堆叠中的微凸块间距从40μm缩小到25μm,下一代将进一步缩至10μm以下;

- TCB(热压键合):大面积芯片的热压键合需要在整个芯片面积上保持均匀的温度和压力分布,偏差不得超过±1℃和±0.5N。

这意味着封装设备的定位系统、光学对准系统和运动控制系统都需要进行根本性的升级。一台先进封装键合设备的对准系统精度,已经接近光刻机的要求。

2.2 翘曲控制:薄晶圆与大基板的热应力博弈

先进封装中的翘曲(Warpage)问题是一个系统性挑战。当多颗芯片通过硅中介层组装在有机基板上时,不同材料之间的热膨胀系数(CTE)差异会在加热和冷却过程中产生巨大的热应力:

- 硅的CTE约为2.6 ppm/℃

- 有机基板的CTE约为15-17 ppm/℃

- 铜的CTE约为17 ppm/℃

在CoWoS封装中,面积超过5000mm²的硅中介层在回流焊接过程中(峰值温度约260℃)可能产生超过500μm的翘曲变形。HBM堆叠中,经过TSV工艺后减薄至50μm以下的DRAM晶圆更是极易碎裂。封装设备必须具备精密的温度梯度控制和实时翘曲补偿能力,这对设备的热管理子系统和控制算法提出了极高要求。

2.3 良率压力:从”允许失败”到”不能失败”

先进封装的成本结构与传统封装截然不同。一颗采用CoWoS封装的AI芯片,仅封装成本就可能超过1000美元,加上内部集成的GPU die和HBM堆栈,单颗封装成品的物料成本可达数千美元。这意味着:

- 传统封装中1%-2%的良率损失或许可以接受,但在先进封装中,每0.1%的良率损失都意味着巨额的经济损失;

- 封装设备的工艺稳定性——即批次间一致性(Lot-to-Lot Consistency)和机台间一致性(Tool-to-Tool Matching)——变得前所未有地重要;

- KGD(Known Good Die)筛选的准确性直接影响封装良率,上游测试设备和封装设备之间的数据联动成为刚需。

2.4 3D堆叠后的检测”黑箱”

当芯片堆叠到第8层、第12层甚至第16层时,传统的光学检测和X-ray检测都面临严峻挑战。TSV的空洞缺陷(Void)、微凸块的桥接(Bridging)和开路(Open)缺陷、层间的分层(Delamination)——这些隐藏在堆叠结构内部的缺陷,需要更高分辨率、更大穿透深度的检测手段。SAT(超声扫描显微镜)、高能X-ray CT等技术正在被引入,但检测速度和产线节拍的矛盾仍然突出。

三、封装设备的调机困局:传统方法正在失效

先进封装设备的工艺调机(Process Tuning)正面临一场”完美风暴”。

首先,新材料带来了更窄的工艺窗口。混合键合技术要求铜表面的粗糙度控制在0.5nm以下,低温无铅焊料(如Sn-Ag-Cu合金)的回流温度窗口仅有±3℃。新型底部填充材料(Underfill)的固化参数同样极为敏感——温度偏差2℃就可能导致固化不完全或局部应力过大。这些窄窗口意味着设备的每一个工艺参数都必须精确到位。

其次,传统DOE(实验设计)方法的代价变得不可承受。在传统封装中,工程师可以用数百片晶圆进行全因子DOE实验,因为单片成本仅几美元到几十美元。但在先进封装中,一片HBM基板的成本可能高达数百美元,一次完整的CoWoS工艺验证可能需要消耗价值数十万美元的物料。传统的全因子实验设计需要的实验次数随参数数量呈指数增长——5个参数、每个3水平就需要243次实验,这在先进封装中几乎不可能实现。

这正是AI驱动的智能DOE(Smart DOE)技术的价值所在。以迈烁集芯的NeuroBox E5200为例,其核心思路是利用机器学习模型替代传统的统计DOE方法:

- 基于贝叶斯优化的自适应实验设计:系统根据已有实验结果动态选择下一组最有价值的参数组合,而非按照预设的正交表逐一执行;

- 迁移学习:将同类设备、相似工艺上的历史数据作为先验知识,大幅减少新工艺的探索空间;

- 多目标优化:同时优化键合强度、翘曲量、位置精度等多个目标,找到全局最优解而非局部最优。

在实际应用中,Smart DOE可以将传统需要200-300次实验才能完成的工艺优化,压缩到40-60次,试片成本降低约80%,调机周期从数周缩短至数天。对于先进封装设备厂商和封装代工厂而言,这不仅仅是成本节省,更是抢占市场时间窗口的关键——在AI算力芯片供不应求的当下,谁能更快完成设备调机和工艺验证,谁就能更早交付产能。

四、封装产线的AI控制需求:从”事后检测”到”实时预防”

先进封装产线的挑战不仅在于调机阶段,量产运行中的工艺控制同样至关重要。

与前道晶圆制造类似,封装设备普遍支持SECS/GEM通讯协议,可以实时采集设备状态数据和工艺参数。一台典型的热压键合设备在每次键合过程中会产生包括键合力曲线、温度曲线、Z轴位移曲线、真空度变化等在内的数十个时间序列参数。这些数据构成了AI产线控制的基础。

封装产线的AI控制需求主要体现在三个层面:

虚拟量测(VM,Virtual Metrology):在先进封装中,许多关键质量指标(如微凸块的接合强度、TSV的电阻值)无法进行100%在线检测,只能通过抽检获得。VM技术利用设备实时工艺数据建立预测模型,在不增加检测工序的前提下,对每一颗产品的质量进行实时预估。对于HBM堆叠来说,这意味着可以在键合完成后立即判断该堆栈是否存在潜在风险,而非等到最终测试才发现问题。

逐次控制(R2R,Run-to-Run Control):封装设备的工艺参数会随着使用时间、耗材损耗、环境变化而漂移。R2R控制系统在每一次(或每一批次)生产结束后,根据实际结果自动微调下一次的工艺参数设定值,将工艺状态始终维持在最优窗口内。在键合设备上,这可能表现为自动补偿键合头的磨损带来的压力变化,或者根据环境温湿度调整预热参数。

故障检测与分类(FDC,Fault Detection & Classification):实时监测设备运行数据中的异常模式,在工艺偏移演变为良率损失之前及时预警。对于价值极高的先进封装产品,FDC的灵敏度和误报率平衡尤为关键——漏检一次可能损失数万美元的产品,但频繁误报又会严重影响设备利用率。

迈烁集芯的NeuroBox E3200正是面向这一场景的边缘AI控制平台。E3200部署在产线设备侧,通过SECS/GEM协议实时采集设备数据,在边缘端完成VM预测、R2R参数调整和FDC异常检测。相比将数据上传至云端处理的方案,边缘AI的核心优势在于低延迟——对于键合设备这类需要毫秒级响应的场景,边缘计算架构可以确保控制指令在10ms以内下发,满足产线实时性要求。同时,E3200支持多台设备间的数据联动,实现跨设备的工艺一致性管理——当封装产线同时运行数十台同型号键合设备时,确保任意一台设备的产品质量都在规格范围内。

五、展望:AI与先进封装的深度融合

站在2026年的时间节点回望,先进封装已经从一个”后端配角”演变为决定AI芯片性能上限的”前台主角”。展望未来,我们认为以下趋势值得关注:

封装与设计的协同优化(Co-optimization):未来的Chiplet架构设计将在EDA阶段就纳入封装约束——不仅是热、电、力学的物理约束,还包括封装设备的工艺能力边界。AI将在这种跨域协同优化中发挥不可替代的作用,帮助设计师在数十亿个设计-封装参数组合中快速找到全局最优解。

自适应封装产线:随着Chiplet架构下产品组合日益多样化,封装产线需要在不同产品之间快速切换。AI驱动的自适应控制系统将使设备能够根据产品类型自动加载最优工艺配方,并在运行过程中实时优化,大幅减少产品切换的downtime和试产损耗。

数字孪生与预测性维护:先进封装设备的精密机械部件(如键合头、真空吸嘴、加热平台)的劣化直接影响工艺精度。基于AI的数字孪生模型将能够根据设备运行数据实时评估部件状态,在精度劣化到影响产品质量之前主动安排维护,将非计划停机率降低50%以上。

全流程良率闭环:从晶圆制造、KGD测试到封装组装、最终测试,AI将打通全流程的数据链路,建立端到端的良率预测和根因分析模型。当封装测试发现异常时,系统可以在数分钟内追溯到具体的工艺偏移环节,而非依赖工程师数天甚至数周的人工排查。

先进封装的技术挑战是真实而严峻的,但这恰恰意味着巨大的创新机会。在这场技术变革中,AI不是锦上添花的工具,而是突破瓶颈的关键力量。无论是设备调机阶段的智能DOE,还是量产阶段的实时工艺控制,AI正在为先进封装产业注入全新的效率范式。